The STM32's independent watchdog is driven by an internal dedicated 40Khz low-speed clock that is effective even if the main clock fails. It should be noted here that the independent watchdog's clock is an internal RC clock, so it is not an accurate 40Khz, but a variable clock between 30 and 60Khz, but we calculate it at a frequency of 40Khz when estimating. The watchdog's time requirements are not very accurate, so the clock is somewhat biased and acceptable.

First we have to explain the principle of the watchdog. Let us summarize:

Under the interference of the external system, the phenomenon that the program runs away will lead to an infinite loop. The watchdog circuit is to avoid this situation. The role of the watchdog is to realize the automatic reset and restart of the processor (send the reset signal) after receiving the dog signal (indicating that the MCU has been hung) within a certain period of time (through the timer counter).

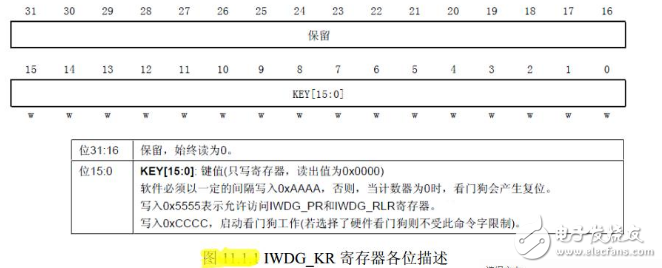

Below we will understand how to implement the configuration through the library function after understanding several registers associated with the independent watchdog.The first is the key value register IWDG_KR, the description of each bit of the register is as shown:

Write 0xCCCC in the key value register (IWDG_KR) to start enabling the independent watchdog; at this point the counter starts counting down from its reset value of 0xFFF. When the counter counts to the end 0x000, a reset signal (IWDG_RESET) is generated. Whenever 0xAAAA is written to the key register IWDG_KR, the value in IWDG_RLR is reloaded into the counter to avoid a watchdog reset. The IWDG_PR and IWDG_RLR registers are write protected. To modify the values ​​of these two registers, you must first write 0x5555 to the IWDG_KR register. Writing other values ​​to this register will disrupt the sequence of operations and the registers will be reprotected. The reload operation (ie writing 0xAAAA) also initiates write protection.

There are also two registers, a prescaler register (IWDG_PR), which is used to set the division factor of the watchdog clock. Another reload register. This register is used to hold the value reloaded into the counter. This register is also a 32-bit register, but only the lower 12 bits are valid.

As long as the above three registers are set accordingly, we can start the independent watchdog of STM32. The boot process can be implemented as follows (the independent watchdog related library functions and definitions are distributed in the files stm32f10x_iwdg.h and stm32f10x_iwdg.c Medium):

1) Cancel register write protection (write 0X5555 to IWDG_KR)

Through this step, we cancel the write protection of IWDG_PR and IWDG_RLR so that the two registers can be manipulated later to set the values ​​of IWDG_PR and IWDG_RLR. The implementation functions in the library function are:

IWDG_WriteAccessCmd(IWDG_WriteAccess_Enable);

This function is very simple, as the name suggests is to open / cancel write protection, that is, enable / disable write permission.

2) Set the prescaler and reload values ​​of the independent watchdog

The function to set the watchdog's division factor is:

Void IWDG_SetPrescaler(uint8_t IWDG_Prescaler); //Set the IWDG prescaler value

The function to set the reload value of the watchdog is:

Void IWDG_SetReload(uint16_t Reload); //Set IWDG reload value

Set the watchdog's crossover coefficient prr and reload value to know the dogdog's dog feed time (that is, the watchdog timeout). This time is calculated as:

Tout=((4&TImes;2^prer) &TImes;rlr) /40

Tout is the watchdog overflow time (in ms); prer is the watchdog clock prescaler value (IWDG_PR value), the range is 0~7; rlr is the watchdog reload value (IWDG_RLR value);

For example, if we set the prer value to 4 and the rlr value to 625, then we can get Tout=64&TImes;625/40=1000ms, so that the watchdog's overflow time is 1s, as long as you are within one second, once Writing 0XAAAA to IWDG_KR will not cause a watchdog reset (it is also possible to write multiple times). Here you need to remind everyone that the watchdog's clock is not accurate 40Khz, so when feeding the dog, it is best not to be too late, otherwise, there may be a watchdog reset.

3) Reload the count value to feed the dog (write 0XAAAA to IWDG_KR)

The function that overrides the count value in a library function is:

IWDG_ReloadCounter(); //Reload the IWDG counter according to the value of the IWDG reload register

With this sentence, STM32 will reload the value of IWDG_RLR into the watchdog counter. That is, the dog feeding operation of the independent watchdog is realized.

4) Start the watchdog (write 0XCCCC to IWDG_KR)

The function that starts the independent watchdog in the library function is:

IWDG_Enable(); //Enable IWDG

Use this sentence to start the STM32 watchdog. Note that IWDG can no longer be turned off once it is enabled! Want to close, can only restart, and can not open IWDG after restart, otherwise the problem is still, so here to remind everyone, if you do not use IWDG, do not open it, to avoid trouble.

Residential Energy Storage System

Enershare's commitment to future-ready energy solutions for smart home innovations, Enershare`s Energy Storage Systems create a flexible energy maintenance system for homeowners who want to take more control of their home energy use, it is intended to be used for home battery energy storage and stores electricity for solar self-consumption, load shifting, backup power, and off-the-grid use. you can use it anytime you want-at night or during an outage.

Home Battery,Home Battery Backup,Home Energy Storage System,Battery Backup Power Supply For Home,High Capacity Electrical Backup,Power Bank For Home

Shenzhen Enershare Technology Co.,Ltd , https://www.enersharepower.com